прадукты Катэгорыя

- FM-перадатчык

- 0-50w 50w-1000w 2kw-10kw 10kw +

- ТБ перадатчык

- 0-50w 50-1kw 2kw-10kw

- антэна FM

- ТБ антэны

- антэна аксэсуар

- кабель злучальнік разветвитель харчавання эквівалентная нагрузка

- RF Transistor

- крыніца харчавання

- аўдыё абсталяванне

- DTV Front End абсталяванне

- сістэма Link

- сістэма STL Сістэма Link Мікрахвалевая печ

- FM-радыё

- вымяральнік магутнасці

- іншыя прадукты

- Спецыяльна для каранавіруса

прадукты Тэгі

Fmuser Сайты

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> афрыкаанс

- sq.fmuser.net -> албанская

- ar.fmuser.net -> арабская

- hy.fmuser.net -> Армянскі

- az.fmuser.net -> азербайджанскі

- eu.fmuser.net -> баскская

- be.fmuser.net -> Беларуская

- bg.fmuser.net -> Балгарская

- ca.fmuser.net -> каталонская

- zh-CN.fmuser.net -> кітайскі (спрошчаны)

- zh-TW.fmuser.net -> Кітайскі (традыцыйны)

- hr.fmuser.net -> харвацкая

- cs.fmuser.net -> чэшская

- da.fmuser.net -> дацкая

- nl.fmuser.net -> Галандская

- et.fmuser.net -> эстонская

- tl.fmuser.net -> філіпінская

- fi.fmuser.net -> фінская

- fr.fmuser.net -> Французская

- gl.fmuser.net -> галісійская

- ka.fmuser.net -> грузінскі

- de.fmuser.net -> нямецкая

- el.fmuser.net -> Грэчаскі

- ht.fmuser.net -> Гаіцянскі крэол

- iw.fmuser.net -> іўрыт

- hi.fmuser.net -> хіндзі

- hu.fmuser.net -> Венгерская

- is.fmuser.net -> ісландская

- id.fmuser.net -> інданезійская

- ga.fmuser.net -> ірландскі

- it.fmuser.net -> Італьянская

- ja.fmuser.net -> японскі

- ko.fmuser.net -> карэйская

- lv.fmuser.net -> латышскі

- lt.fmuser.net -> Літоўскі

- mk.fmuser.net -> македонская

- ms.fmuser.net -> малайская

- mt.fmuser.net -> мальтыйская

- no.fmuser.net -> Нарвежскі

- fa.fmuser.net -> персідская

- pl.fmuser.net -> польская

- pt.fmuser.net -> партугальская

- ro.fmuser.net -> Румынская

- ru.fmuser.net -> руская

- sr.fmuser.net -> сербская

- sk.fmuser.net -> славацкая

- sl.fmuser.net -> Славенская

- es.fmuser.net -> іспанская

- sw.fmuser.net -> суахілі

- sv.fmuser.net -> шведская

- th.fmuser.net -> Тайская

- tr.fmuser.net -> турэцкая

- uk.fmuser.net -> украінскі

- ur.fmuser.net -> урду

- vi.fmuser.net -> В'етнамская

- cy.fmuser.net -> валійская

- yi.fmuser.net -> Ідыш

Што такое Half Adder: Схема і яе прымяненне

Date:2021/10/18 21:55:58 Hits:

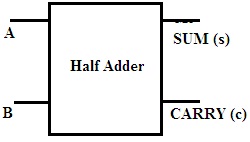

Half Adder - гэта тып асноўнай лічбавай схемы. Раней у аналагавых схемах выконваліся розныя аперацыі. Пасля адкрыцця лічбавай электронікі ў ёй праводзяцца аналагічныя аперацыі. Лічбавыя сістэмы лічацца эфектыўнымі і надзейнымі. Сярод розных аперацый адна з найбольш прыкметных аперацый - гэта арыфметыка. Яна ўключае ў сябе складанне, адніманне, множанне і дзяленне. Аднак ужо вядома, што гэта можа быць кампутар, любы электронны гаджэт, напрыклад калькулятар, можа выконваць матэматычныя аперацыі. Гэтыя аперацыі складаюцца з двайковых значэнняў. Гэта магчыма дзякуючы наяўнасці ў ім пэўных схем. Гэтыя схемы называюцца бінарнымі складальнікамі і адымальнікамі. Гэты тып схем прызначаны для двайковых кодаў, кодаў Excess-3 і іншых кодаў. Далей бінарныя складальнікі класіфікуюцца на два тыпу. Яны ўяўляюць сабой: напалову складальнік і поўнае складанне Што такое напалову сціскальнік? Лічбавая электронная схема, якая функцыянуе для складання двайковых лікаў, вызначаецца як напалову складальнік. Працэс складання з'яўляецца дэнарскім, адзінае адрозненне - абраная сістэма злічэння. У двайковай сістэме нумарацыі існуюць толькі 0 і 1. Вага ліку цалкам залежыць ад пазіцый двайковых лічбаў. Сярод гэтых 1 і 0, 1 разглядаецца як найбольшая лічба, а 0 - як меншая. Структурная схема гэтага суматара Палова складальніка Палова складальніка складаецца з двух уваходаў і вырабляе два выхады. Лічыцца самай простай лічбавай схемай. Уваходнымі дадзенымі гэтай схемы з'яўляюцца біты, па якіх трэба дадаць. Атрыманыя вынікі - гэта сума і перанос.

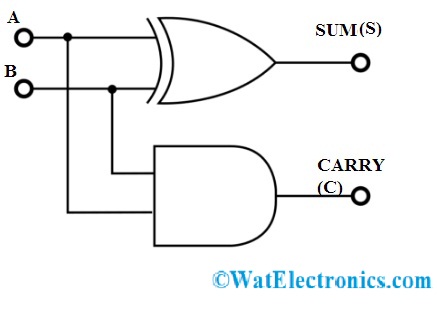

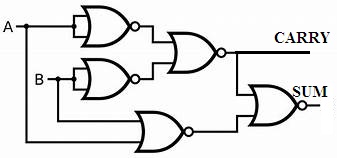

Палова складальніка Палова складальніка складаецца з двух уваходаў і вырабляе два выхады. Лічыцца самай простай лічбавай схемай. Уваходнымі дадзенымі гэтай схемы з'яўляюцца біты, па якіх трэба дадаць. Атрыманыя вынікі - гэта сума і перанос.  Схема гэтага суматара складаецца з двух варот. Гэта вароты AND і XOR. Прыкладзеныя ўваходы аднолькавыя для абодвух варот, якія прысутнічаюць у ланцугу. Але вывад бярэцца з кожнай брамы. Выхад XOR -засаўкі называецца SUM, а вынік AND вядомы. CARRY. Half Adder Truth TableTo Для атрымання адносін вываду, атрыманага да прыкладзенага ўваходу, можна прааналізаваць з дапамогай табліцы, вядомай як табліца ісціны.

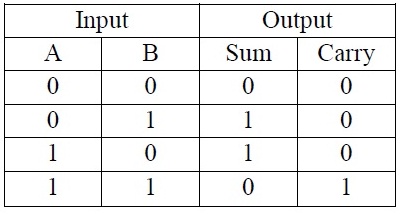

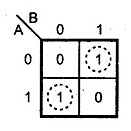

Схема гэтага суматара складаецца з двух варот. Гэта вароты AND і XOR. Прыкладзеныя ўваходы аднолькавыя для абодвух варот, якія прысутнічаюць у ланцугу. Але вывад бярэцца з кожнай брамы. Выхад XOR -засаўкі называецца SUM, а вынік AND вядомы. CARRY. Half Adder Truth TableTo Для атрымання адносін вываду, атрыманага да прыкладзенага ўваходу, можна прааналізаваць з дапамогай табліцы, вядомай як табліца ісціны. Табліца праўды напалову адэдраў З прыведзенай вышэй табліцы ісцін відавочныя наступныя моманты: Калі A = 0, B = 0, абодва прымяняюцца ўваходы роўныя 0. Тады абодва выхаду SUM і CARRY роўныя 0. Сярод двух уваходаў, калі хто -небудзь уваход 1, то сума будзе b e1, але CARRY 0. Калі абодва ўваходу 1, то сума будзе роўная 0, а CARRY будзе роўная 1. На падставе прымяняемых уваходаў палова суматара працягвае аперацыю Ураўненне для гэтага тыпу схем можна рэалізаваць з дапамогай паняццяў Сумы прадуктаў (SOP) і Суммавых прадуктаў (POS). Булевае ўраўненне для гэтага тыпу схем вызначае суадносіны паміж ужытымі ўваходамі і атрыманымі вывадамі. Для вызначэння ўраўнення k-карты складаюцца на аснове значэнняў табліцы ісцін. Ён складаецца з двух раўнанняў, таму што ў ім выкарыстоўваюцца два лагічныя вароты

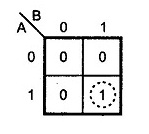

Табліца праўды напалову адэдраў З прыведзенай вышэй табліцы ісцін відавочныя наступныя моманты: Калі A = 0, B = 0, абодва прымяняюцца ўваходы роўныя 0. Тады абодва выхаду SUM і CARRY роўныя 0. Сярод двух уваходаў, калі хто -небудзь уваход 1, то сума будзе b e1, але CARRY 0. Калі абодва ўваходу 1, то сума будзе роўная 0, а CARRY будзе роўная 1. На падставе прымяняемых уваходаў палова суматара працягвае аперацыю Ураўненне для гэтага тыпу схем можна рэалізаваць з дапамогай паняццяў Сумы прадуктаў (SOP) і Суммавых прадуктаў (POS). Булевае ўраўненне для гэтага тыпу схем вызначае суадносіны паміж ужытымі ўваходамі і атрыманымі вывадамі. Для вызначэння ўраўнення k-карты складаюцца на аснове значэнняў табліцы ісцін. Ён складаецца з двух раўнанняў, таму што ў ім выкарыстоўваюцца два лагічныя вароты  K-Map AND Gate Выходнае ўраўненне CARRY атрымана з AND gate.C = A.B Булевы выраз для SUM рэалізуецца ў форме SOP. Такім чынам, K-карта для SUM

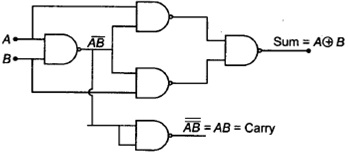

K-Map AND Gate Выходнае ўраўненне CARRY атрымана з AND gate.C = A.B Булевы выраз для SUM рэалізуецца ў форме SOP. Такім чынам, K-карта для SUM K-карта для сумы (XOR) Вырашанае ўраўненне S = A⊕ B Прыкладанні Прыкладанні гэтага асноўнага суматара заключаюцца ў наступным: Для выканання дапаўненняў па двайковых бітах адзінка арыфметыкі і лагікі, прысутная ў кампутары, аддае перавагу гэтай схеме складання. да фарміравання схемы поўнага зліцця. Гэтыя лагічныя схемы з'яўляюцца пераважнымі пры распрацоўцы калькулятараў. Для вылічэння адрасоў і табліц гэтыя схемы з'яўляюцца пераважнымі. Замест толькі складання, гэтыя схемы здольныя апрацоўваць розныя прыкладання ў лічбавых схемах. Акрамя таго, гэта становіцца сэрцам лічбавай электронікі. VHDL -код VHDL -код для ланцуга Half Adder - гэта бібліятэка ieee; выкарыстоўвайце ieee.std_logic_1164.all; сутнасць half_adder isport (a, b: у бітах; сума, выносьце: біт вываду); канец half_adder ; архітэктурныя дадзеныя палова_пастаўшчыка isbeginsum <= a xor b; пераносіць <= a і b; канчатковыя дадзеныя; FAQ1. Што вы маеце на ўвазе пад Adder? Лічбавыя схемы, адзінай мэтай якіх з'яўляецца злучэнне, вядомыя як складальнікі. Гэта асноўныя кампаненты ALU. Складальнікі працуюць у дадатак да розных фарматаў лічбаў. Вывадамі складальнікаў з'яўляюцца сума і перанос.2. Якія абмежаванні напалову складальніка? Біт пераносу, створаны з папярэдняга біта, нельга дадаць - гэта абмежаванне гэтага суматара. Для выканання складання для некалькіх бітаў гэтыя схемы не могуць быць пераважней. Як рэалізаваць Half Adder з дапамогай NOR Gate? Рэалізацыю гэтага тыпу суматара можна таксама зрабіць з дапамогай варотаў NOR. Гэта яшчэ адна Універсальная брама.

K-карта для сумы (XOR) Вырашанае ўраўненне S = A⊕ B Прыкладанні Прыкладанні гэтага асноўнага суматара заключаюцца ў наступным: Для выканання дапаўненняў па двайковых бітах адзінка арыфметыкі і лагікі, прысутная ў кампутары, аддае перавагу гэтай схеме складання. да фарміравання схемы поўнага зліцця. Гэтыя лагічныя схемы з'яўляюцца пераважнымі пры распрацоўцы калькулятараў. Для вылічэння адрасоў і табліц гэтыя схемы з'яўляюцца пераважнымі. Замест толькі складання, гэтыя схемы здольныя апрацоўваць розныя прыкладання ў лічбавых схемах. Акрамя таго, гэта становіцца сэрцам лічбавай электронікі. VHDL -код VHDL -код для ланцуга Half Adder - гэта бібліятэка ieee; выкарыстоўвайце ieee.std_logic_1164.all; сутнасць half_adder isport (a, b: у бітах; сума, выносьце: біт вываду); канец half_adder ; архітэктурныя дадзеныя палова_пастаўшчыка isbeginsum <= a xor b; пераносіць <= a і b; канчатковыя дадзеныя; FAQ1. Што вы маеце на ўвазе пад Adder? Лічбавыя схемы, адзінай мэтай якіх з'яўляецца злучэнне, вядомыя як складальнікі. Гэта асноўныя кампаненты ALU. Складальнікі працуюць у дадатак да розных фарматаў лічбаў. Вывадамі складальнікаў з'яўляюцца сума і перанос.2. Якія абмежаванні напалову складальніка? Біт пераносу, створаны з папярэдняга біта, нельга дадаць - гэта абмежаванне гэтага суматара. Для выканання складання для некалькіх бітаў гэтыя схемы не могуць быць пераважней. Як рэалізаваць Half Adder з дапамогай NOR Gate? Рэалізацыю гэтага тыпу суматара можна таксама зрабіць з дапамогай варотаў NOR. Гэта яшчэ адна Універсальная брама. Палова Adder з выкарыстаннем NOR gates4. Як рэалізаваць Half Adder з дапамогай NAND Gate? Вароты NAND - адзін з відаў універсальных варот. Гэта паказвае на тое, што любое праектаванне схем магчыма з дапамогай засаўкі NAND.

Палова Adder з выкарыстаннем NOR gates4. Як рэалізаваць Half Adder з дапамогай NAND Gate? Вароты NAND - адзін з відаў універсальных варот. Гэта паказвае на тое, што любое праектаванне схем магчыма з дапамогай засаўкі NAND. Палова Adder З прыведзенай вышэй схемы вываз пераносу можа быць створаны шляхам прымянення вываду аднаго засаўкі NAND да ўваходу ў якасці іншых засаўкі NAND. Гэта не што іншае, як знаёмства з высновамі, атрыманымі з AND gate.Выходнае ўраўненне SUM можа быць створана шляхам прымянення вываду першапачатковага засаўкі NAND разам з асобнымі ўваходамі A і B да далейшых варот NAND. Нарэшце, вынікі, атрыманыя гэтымі варотамі NAND, зноў прымяняюцца да засаўкі. Такім чынам, вывад для SUM генеруецца. Таму асноўны суматар у лічбавай схеме можа быць распрацаваны з дапамогай розных лагічных затвораў. Але складанне некалькіх бітаў ўскладняецца і лічыцца абмежаваннем напалову суматара. Ці можаце вы апісаць, якая ІС выкарыстоўваецца для аперацыі прырашчэння ў любых практычных лічыльніках?

Палова Adder З прыведзенай вышэй схемы вываз пераносу можа быць створаны шляхам прымянення вываду аднаго засаўкі NAND да ўваходу ў якасці іншых засаўкі NAND. Гэта не што іншае, як знаёмства з высновамі, атрыманымі з AND gate.Выходнае ўраўненне SUM можа быць створана шляхам прымянення вываду першапачатковага засаўкі NAND разам з асобнымі ўваходамі A і B да далейшых варот NAND. Нарэшце, вынікі, атрыманыя гэтымі варотамі NAND, зноў прымяняюцца да засаўкі. Такім чынам, вывад для SUM генеруецца. Таму асноўны суматар у лічбавай схеме можа быць распрацаваны з дапамогай розных лагічных затвораў. Але складанне некалькіх бітаў ўскладняецца і лічыцца абмежаваннем напалову суматара. Ці можаце вы апісаць, якая ІС выкарыстоўваецца для аперацыі прырашчэння ў любых практычных лічыльніках?

Пакінь паведамленне

спіс паведамленняў

Каментары Загрузка ...